基于DSP开发工具实现FIR滤波器的设计方案

16

16

拍明

拍明

原标题:基于DSP开发工具实现FIR滤波器的设计

数字滤波器在数字信号处理的各种应用中发挥着十分重要的作用,他是通过对采样数据信号进行数学运算处理来达到频域滤波的目的。数字滤波器既可以是有限长单脉冲响应(FIR)滤波器也可以是无限长单脉冲响应(IIR)滤波器。在维纳滤波器理论发明的早期,人们使用IIR滤波器,但现在更多是使用FIR滤波器。本文按照Matlab/Simulink/DSP Builder/QuartusⅡ流程,设计一个FIR滤波器。Altera DSP Builder是连接Simulink和QuartusⅡ开发软件的DSP开发工具。在DSP Builder的无缝设计流程中,首先在Matlab软件中进行算法设计,然后在Simulink软件中进行系统集成,最后将设计输出为硬件描述语言(HDL)文件,以便在QuartusⅡ软件中使用。

1 FIR滤波器介绍

1.1 FIR滤波器原理

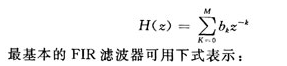

对于一个FIR滤波器系统,他的冲激响应总是有限长的,其系统函数可以记为:

其中:x(n)是输入采样序列;h(n)是滤波器系数;L是滤波器的阶数;y(n)表示滤波器的输出序列。也可以用卷积来表示输出序列y(n)与x(n),h(n)的关系。

y(n)=x(n)*h(n)

典型的直接I型FIR滤波器如图1所示,其输出序列y(n)满足下式:

1.2 设计要求

数字滤波器实际上是一个采用有限精度算法实现的线性非时变离散系统,他的设计步骤是先根据需要确定其性能指标,设计一个系统函数h(n)逼近所需要的性能指标,滤波器的系数的计算可以借助Matlab强大的计算能力和现成的滤波器设计工具来完成,最后采用有限的精度算法实现。本系统的设计指标为,设计一个14阶的FIR滤波器。1 MHz和16 MHz的两个正弦波的合成波形,经过这个滤波器,滤除16 MHz的成分。

2 DSP Builder设计流程

使用DSP Builder完成设计时,首先在Matlab/Simulink软件中建立模型文件(.mdl),DSP Builder SignalCom-piler模块读取由DSP Builder和MegaCore模块构建的Simulink建模文件(.mdl),生成VHDL文件和工具命令语言(Tcl)脚本,进行综合、硬件实施和仿真。

3 FIR数字滤波器的DSP Builder设计

3.1 Matlab/Simulink建模

根据FIR数字滤波器的算法,在Matlab的Simulink环境中建立一个MDL模型文件。用图形方式调用Alter-aDSPBuilder和其他的Simulink库中的图形模块。

3.2 在Simulink中仿真并生成VHDL代码

完成模型设计之后,可以先在Simulink中对模型进行仿真,可以通过Simulink中的示波器模块查看各步骤的中间结果。输入信号采用频率为1 MHz和16 MHz的两个正弦波的叠加。仿真结果如图2所示。从仿真波形可以看出,经过FIR滤波器之后,16 MHz的高频信号被很好地滤除了。

3.3 使用Modelsim进行RTL仿真

在Simulink中进行的仿真是属于系统验证性质的,是对mdl文件进行仿真,并没有对生成的VHDL代码进行过仿真。事实上,生成VHDL描述的是RTL级的,是针对具体的硬件结构的,而在Matlab的Simulink中的模型仿真是算法级的,两者之间有可能存在软件理解上的差异。转换后的VHDL代码实现可能与mdl模型描述的情况不完全相符。这就需要针对生成的RTL级VHDL代码进行功能仿真,如图3所示。

仿真结果说明,本滤波器可以较好地起到滤波的效果,由于输入正弦波经过数字化过程之后在Modelsim中还原出的模拟波形出现失真现象。

3.4 使用QuartusⅡ进行时序仿真和综合编译

Modelsim完成的RTL级仿真只是功能仿真,其仿真结果并不能精确地反映电路的全部硬件特性,进行门级的时序仿真仍然是十分重要的。时序仿真即针对具体硬件芯片,在仿真时加入芯片内部的时间信息包括:建立时间,保持时间,关键路径延时等。综合编译后,tsu=4.622 ns,tco=6.925 ns,th=0.415 ns,时间分析符合实际情况。

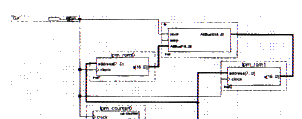

4 滤波器设计在FPGA上的实现

由于从Simulink建模仿真,到Modelsim RTL仿真和QuartusⅡ时序仿真,使用的输入正弦波都是仿真信号,而不是实际的信号源。在硬件实际运行时,可以从外部信号源接入芯片内部或者在芯片内部存储正弦波的数据。这里采用的是后者,即在顶层文件中引入LPM_ROM宏模块,在其中存入正弦波数据的mif文件(存储初始化文件),FIR滤波器模块直接从ROM中读取数据,经过滤波处理之后数据存入另一ROM中,可以通过In-systemmemory content editor工具从中读出数据,再利用Matlab还原出波形,从而在实际硬件中验证了滤波器的功能。

实现的顶层图如图4所示。

5 结 语

本文采用Matlab/Simulink/DSP Builder/QuartusⅡ的设计流程,实现了14阶FIR滤波器。通过系统仿真,RTL仿真,时序仿真和实际硬件测试(这里采用了一种不需要使用SignaltapⅡ软件逻辑分析仪的方法)对滤波器的功能、性能等进行了分析,从而验证了采用DSP,Builder实现滤波器设计的硬件化的独特优势。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)