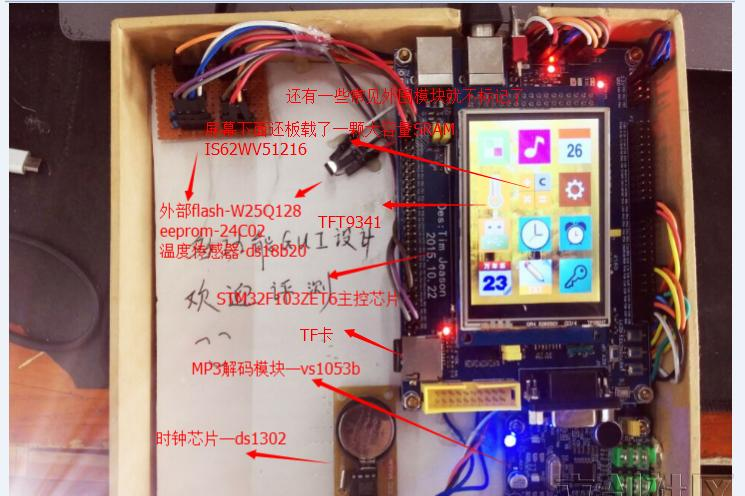

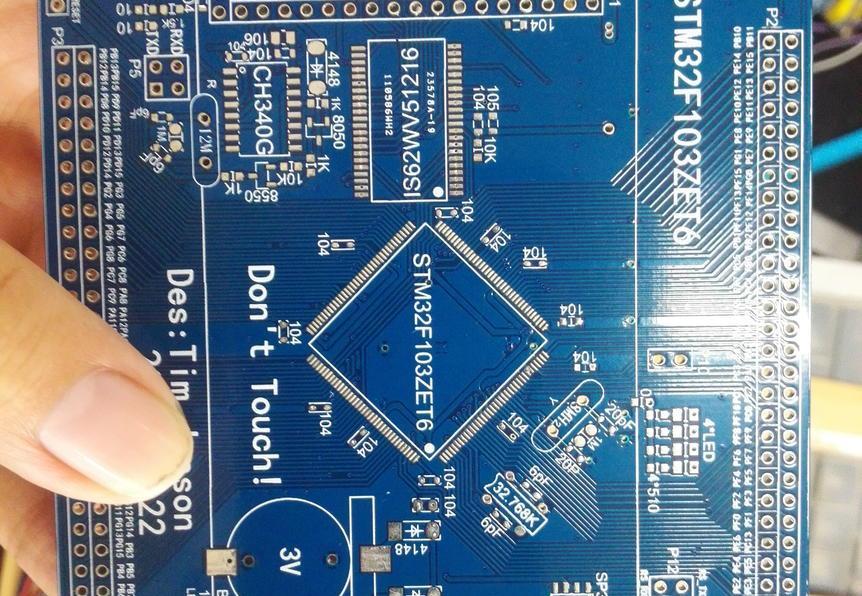

基于STM32F103ZET6+IS62WV51216+TFT9341的多功能GUI系统源码及电路设计方案

252

252

拍明

拍明

原标题:【毕业设计】-基于STM32多功能GUI系统源码及电路

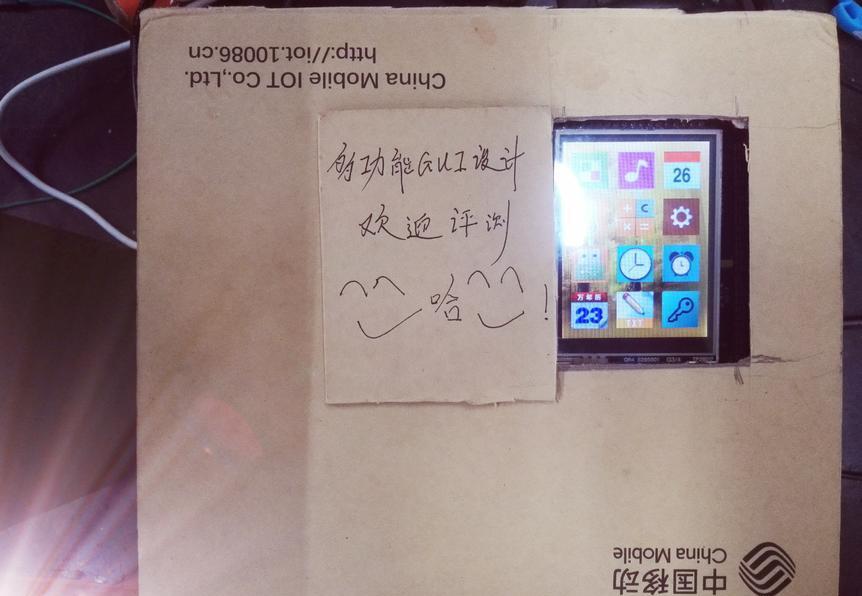

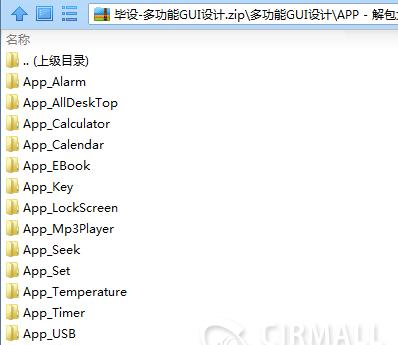

设计了一款基于STM32的多功能GUI设计,功能包括:MP3/WMA/WAV/MIDI音频文件播放器、JPEG/JPG/BMP图片浏览、闹钟、万年历、电子书、温度计、计算器、功率放大等。

整个系统主要由音频解码部分、音效处理部分、SD卡部分、功率放大、电源部分、人机交互等几个部分组成,整个系统由一块MCU(STM32F103ZET6)控制运行,各个部分协调运作,人机交互部分采用LCD和触摸屏实现,输出部分采用2.8寸的240*320的彩色液晶实现,输入部分主要采用触摸屏实现.

采用触摸屏控制,可以方便的控制整个系统,使得整个系统的操作非常的人性化

整个系统涉及方面很多,颇具挑战性,主要难点在与FAT文件系统解析,JPEG/BMP数据格式解析,触摸屏控制等。针对本系统的特点,采用各个击破的方法,来一步步实现以上功能。最终实现整个系统的功能。

GUI系统源码截图:

详细功能介绍戳这:https://club.szlcsc.com/article/details_6620_1.html

毕设演示视频链接: https://v.qq.com/x/page/t0528yx54w5.html

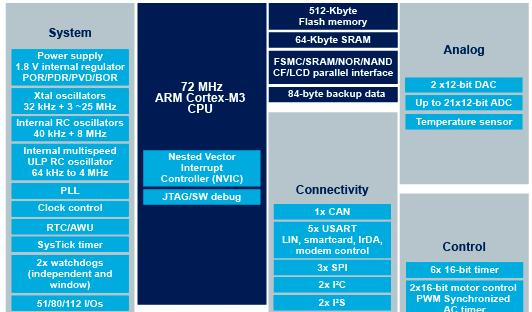

【STM32F103ZET6】

Mainstream Performance line, ARM Cortex-M3 MCU with 512 Kbytes Flash, 72 MHz CPU, motor control, USB and CAN

The STM32F103xC, STM32F103xD and STM32F103xE performance line family incorporates the high-performance ARM® Cortex®-M3 32-bit RISC core operating at a 72 MHz frequency, high-speed embedded memories (Flash memory up to 512 Kbytes and SRAM up to 64 Kbytes), and an extensive range of enhanced I/Os and peripherals connected to two APB buses. All devices offer three 12-bit ADCs, four general-purpose 16-bit timers plus two PWM timers, as well as standard and advanced communication interfaces: up to two I2Cs, three SPIs, two I2Ss, one SDIO, five USARTs, an USB and a CAN.

The STM32F103xC/D/E high-density performance line family operates in the –40 to +105 °C temperature range, from a 2.0 to 3.6 V power supply. A comprehensive set of power-saving mode allows the design of low-power applications.

These features make the STM32F103xC/D/E high-density performance line microcontroller family suitable for a wide range of applications such as motor drives, application control, medical and handheld equipment, PC and gaming peripherals, GPS platforms, industrial applications, PLCs, inverters, printers, scanners, alarm systems video intercom, and HVAC.

主要特性

Core: ARM® 32-bit Cortex®-M3 CPU

72 MHz maximum frequency, 1.25 DMIPS/MHz (Dhrystone 2.1) performance at 0 wait state memory access

Single-cycle multiplication and hardware division

Memories

256 to 512 Kbytes of Flash memory

up to 64 Kbytes of SRAM

Flexible static memory controller with 4 Chip Select. Supports Compact Flash, SRAM, PSRAM, NOR and NAND memories

LCD parallel interface, 8080/6800 modes

Clock, reset and supply management

2.0 to 3.6 V application supply and I/Os

POR, PDR, and programmable voltage detector (PVD)

4-to-16 MHz crystal oscillator

Internal 8 MHz factory-trimmed RC

Internal 40 kHz RC with calibration

32 kHz oscillator for RTC with calibration

Low power

Sleep, Stop and Standby modes

VBAT supply for RTC and backup registers

3 × 12-bit, 1 μs A/D converters (up to 21 channels)

Conversion range: 0 to 3.6 V

Triple-sample and hold capability

Temperature sensor

2 × 12-bit D/A converters

DMA: 12-channel DMA controller

Supported peripherals: timers, ADCs, DAC, SDIO, I2Ss, SPIs, I2Cs and USARTs

Debug mode

Serial wire debug (SWD) & JTAG interfaces

Cortex®-M3 Embedded Trace Macrocell™

Up to 112 fast I/O ports

51/80/112 I/Os, all mappable on 16 external interrupt vectors and almost all 5 V-tolerant

Up to 11 timers

Up to four 16-bit timers, each with up to 4 IC/OC/PWM or pulse counter and quadrature (incremental) encoder input

2 × 16-bit motor control PWM timers with dead-time generation and emergency stop

2 × watchdog timers (Independent and Window)

SysTick timer: a 24-bit downcounter

2 × 16-bit basic timers to drive the DAC

Up to 13 communication interfaces

Up to 2 × I2C interfaces (SMBus/PMBus)

Up to 5 USARTs (ISO 7816 interface, LIN, IrDA capability, modem control)

Up to 3 SPIs (18 Mbit/s), 2 with I2S interface multiplexed

CAN interface (2.0B Active)

USB 2.0 full speed interface

SDIO interface

CRC calculation unit, 96-bit unique ID

ECOPACK® packages

STM32F103ZET6电路原理图

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)